D-триггер

D-триггер — ещё один представитель семейства триггеров. Можно сказать, что это улучшенная версия RS-триггера. Дело в том, что в RS-триггере для установки его в состояние нуля или единицы используются отдельные входы. Но это не всегда удобно, иногда требуется управлять триггером с одного входа. Собственно, эту идею и реализует D-триггер. Он может быть выполнен только в синхронном варианте, и в общем случае, имеет два входа: D - управляющий вход, и C - вход для синхронизирующего импульса. Название D-триггера происходит от слова delay - задержка. Он запоминает, "задерживает" на некоторое время входной сигнал.

Содержание статьи:

- Принцип работы D-триггера

- Таблица истинности D-триггера

- Статический D-триггер

- Динамический D-триггер

- Практическая реализация - микросхема CD4013

- Схема делителя частоты

Принцип работы D-триггера

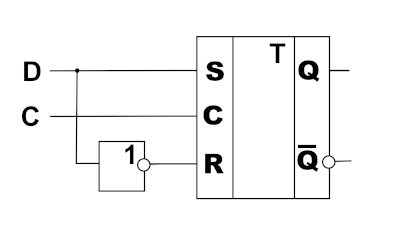

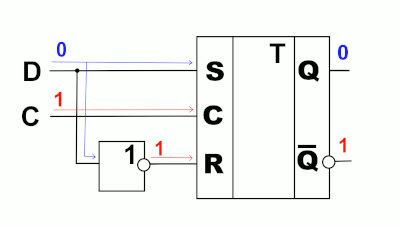

Если Вы ознакомились с устройством RS-триггера, Вы легко поймёте, как его переделать в D-триггер. Обратимся к следующей схеме:

Схема D-триггера на основе RS-триггера

Сигнал со входа D попадает на вход S RS-триггера. И он же инвертируется схемой НЕ и передаётся на вход R. Таким образом, если на входе D единица, то единица будет на входе S, а R будет сидеть на нуле. Когда на входе D ноль, картинка будет зеркальная: R=1, S=0.

В момент появления синхрон-импульса на входе C (а мы помним, что синхронный триггер может поменять состояние только при наличии синхронизирующего импульса), триггер переключится в то состояние, которое в данный момент присутствует на входе D.

Переключение триггера в состояние 0

Таким образом, D-триггер является простейшей ячейкой памяти, которая по синхронизирующему импульсу запоминает значение на D-входе.

Таблица истинности D-триггера

| С | D | Q(t) | Q(t+1) | Примечание |

| 0 | любое | 1 | 1 | Режим хранения информации |

| 0 | любое | 0 | 0 | |

| 1 | 1 | любое | 1 | Режим записи информации |

| 1 | 0 | любое | 0 |

Здесь Q(t) - предыдущее состояние триггера, а Q(t+1) - следующее состояние, наступившее в результате появления на входах заданной комбинации сигналов.

Обратите внимание, в отличие от RS-триггера, у D-триггера нет недопустимых комбинаций сигналов, приводящих к неопределённому состоянию.

Статический D-триггер

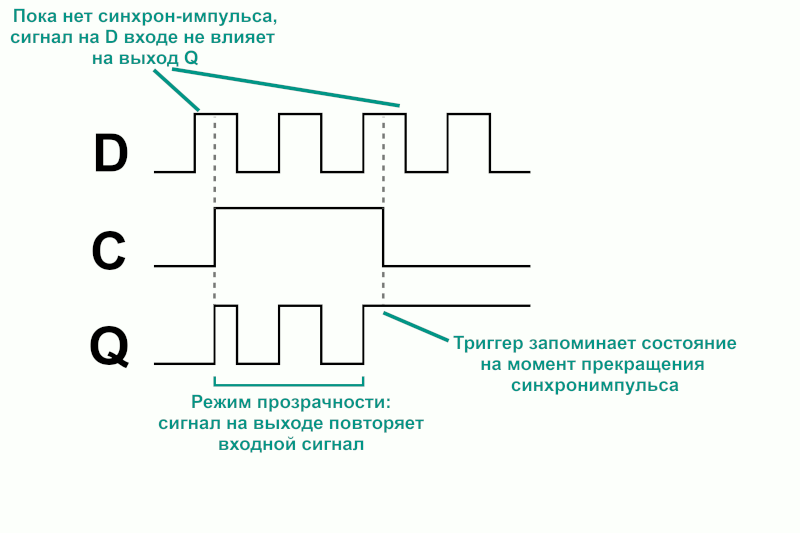

Все синхронные триггеры по типу управления делятся на статические и динамические. В этом смысле D-триггер не является исключением, и выше мы рассмотрели схему статического D-триггера. Дело в том, что, пока на входе C присутствует высокий уровень, выходной сигнал полностью повторяет форму входного. Об этом режиме говорят: триггер является прозрачным. Поэтому, статический D-триггер ещё называют прозрачной защёлкой. Такой триггер запоминает информацию (защёлкивается) в тот момент, когда исчезает потенциал на C-входе.

Чтобы представить это более наглядно, обратимся к временной диаграмме (кликните на картинку для увеличения):

Временная диаграмма статического D-триггера

Динамический D-триггер

Триггеры со статическим управлением не всегда удобны. Они требуют согласования длительности импульсов, поступающих на D и C входы. Если C-импульс окажется длиннее D-импульса, в триггер запишется совсем не то, что ожидается.

Чтобы избежать возможных неопределённостей, синхронизирующие импульсы стараются делать как можно короче по времени. Другой вариант - использовать динамический триггер. Он меняет состояние только в момент перепада напряжения на C-входе. Соответственно, может работать либо по фронту импульса (когда напряжение меняется с 0 на 1), либо, наоборот, по спаду импульса (иногда говорят, по заднему фронту) на синхронизирующем входе.

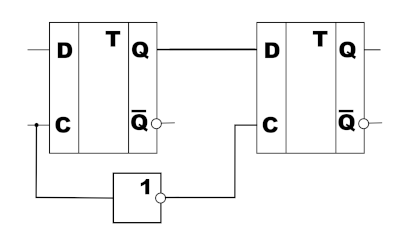

Простейший динамический D-триггер можно собрать из двух статических по следующей схеме:

Схема динамического D-триггера на основе двух статических

Когда на C-вход первого триггера попадает синхронизирующий импульс, первый триггер переходит в режим прозрачности. Но, одновременно синхрон-импульс инвертируется схемой НЕ и переключает второй триггер в режим хранения информации, он не будет менять своё состояние. В момент спада C-импульса первый триггер перейдёт в режим хранения, на его выходе зафиксируется его текущее состояние. А второй триггер как раз перейдёт в режим прозрачности, и передаст это состояние на свой выход.

Таким образом, потенциал на выходе этой схемы может поменяться только в момент спада синхрон-импульса.

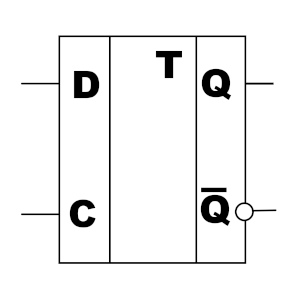

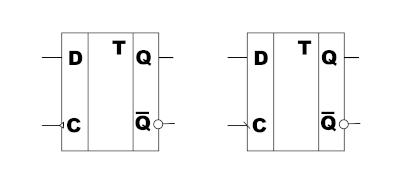

На схемах динамический D-триггер, синхронизируемый по спаду импульса, обозначается следующим образом:

Обозначение динамического D-триггера с синхронизацией по спаду импульса

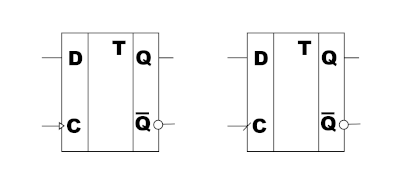

Аналогично можно собрать схему с управлением по фронту импульса, если инвертировать синхронизирующий сигнал не для второго триггера, а для первого. Если D-триггер управляется по фронту импульса, он может обозначаться вот так:

Обозначение динамического D-триггера с синхронизацией по фронту

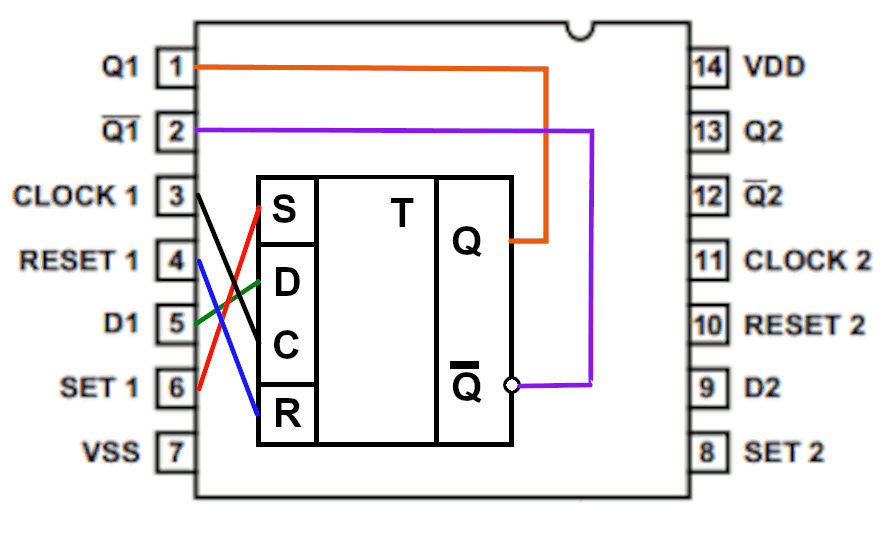

Практическая реализация - микросхема CD4013

Одна из самых распространённых реализаций D-триггера - микросхема CD4013. Её отечественный аналог К561ТМ2. Микросхема содержит два динамических D-триггера, управляемых по фронту:

Нумерация выводов микросхемы CD4013. Показан только один D-триггер из двух.

R и S входы не обязательны для D-триггера, но в данной микросхеме они присутствуют. Причём, работают асинхронно. С их помощью можно переключить триггер в нужное состояние независимо от тактовых импульсов на входе C.

Схема делителя частоты

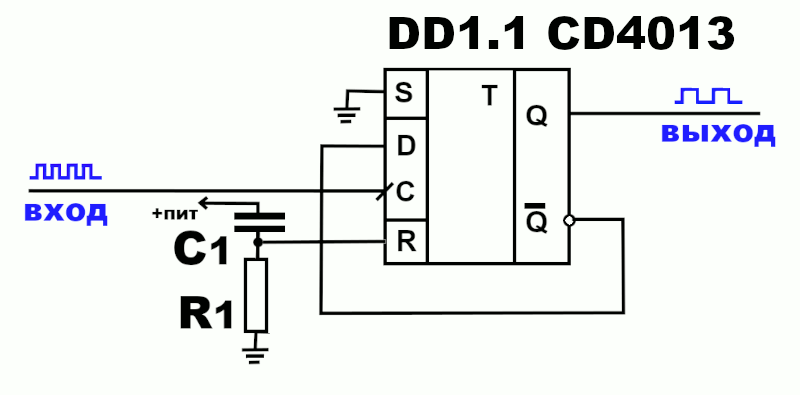

Ниже приведена схема делителя частоты на 2, построенного на D-триггере.

Схема делителя частоты на основе D-триггера

Также на этой схеме можно увидеть стандартное решение для установки начального состояния триггера. Дело в том, что после включения питания при отсутствии внешних импульсов состояние триггеров в микросхеме CD4013 оказывается случайным: либо 0, либо 1. Но иногда требуется, чтобы стартовое состояние было строго определённым. Для этого служит цепочка C1-R1. В начальный момент времени конденсатор разряжен, его сопротивление близко к нулевому. За счёт тока заряда на R-входе триггера возникает высокий потенциал и переключает его в состояние 0. Заряд конденсатора длится очень короткое время, после чего он перестаёт проводить ток и на R-входе установится низкий потенциал через резистор R1. То есть, отработав единажды в момент включения питания, далее цепь R1-C1 уже не влияет на состояние триггера.

Теперь о том, как работает делитель частоты. Если изначально триггер в состоянии 0, то на Q` выходе будет 1, которая попадает на вход D. Поэтому, как только придёт первый же импульс на C-вход, триггер по его фронту переключится в состояние 1. Но тогда уже на Q` появится ноль, который попадёт на D в ожидании следующего синхрон-импульса. Который переключит триггер обратно в состояние 1. Таким образом, нечетные импульсы будут переключать триггер в 1, а чётные - в 0. И частота импульсов на выходе Q окажется в два раза меньше, чем на входе C. Это и есть деление частоты на два.

Если две такие схемы включить последовательно, получится делитель на 4. И так далее.

Комментарии (5)

А как лучше сделать начальную установку Q = D в момент включения питания (D задано аппаратно)?

Или для D-триггера К561ТМ2 это делается автоматически?

Добавить комментарий